Copyright © Dongguan Haoxiang Industrial Investment Co., Ltd. All Rights Reserved. Site Map

- +86-13712992686

- 2826095532@qq.com

- No. 85, Yongjun Second Road, Huangjiang Town, Dongguan City

In the mid-1960s, most semiconductor substrates were polished by mechanical polishing, and the resulting mirror surface was severely damaged. In the 1970s, chemical mechanical polishing (CMP) technology represented by silica sol gradually replaced traditional mechanical polishing. Since the 1990s, with the development of the electronics industry, the demand for silica sol as a raw material for silicon wafer polishing liquid has increased sharply. The so-called polishing agent is composed of silica sol, water, dispersion stabilizer, wetting regulator, pH regulator and surface treatment agent. Silica sol is a polishing material for CMP technology with excellent performance. It can be used for rough polishing and fine polishing of silicon wafers, as well as IC processing. It is particularly suitable for flattening of multi-layered thin films of large-scale integrated circuits. Silica sol can also be used for post-CMP cleaning of wafers and other processing processes of semiconductor devices, flat panel displays, polycrystalline modules, micro-electromechanical systems, optical camera tubes, etc.

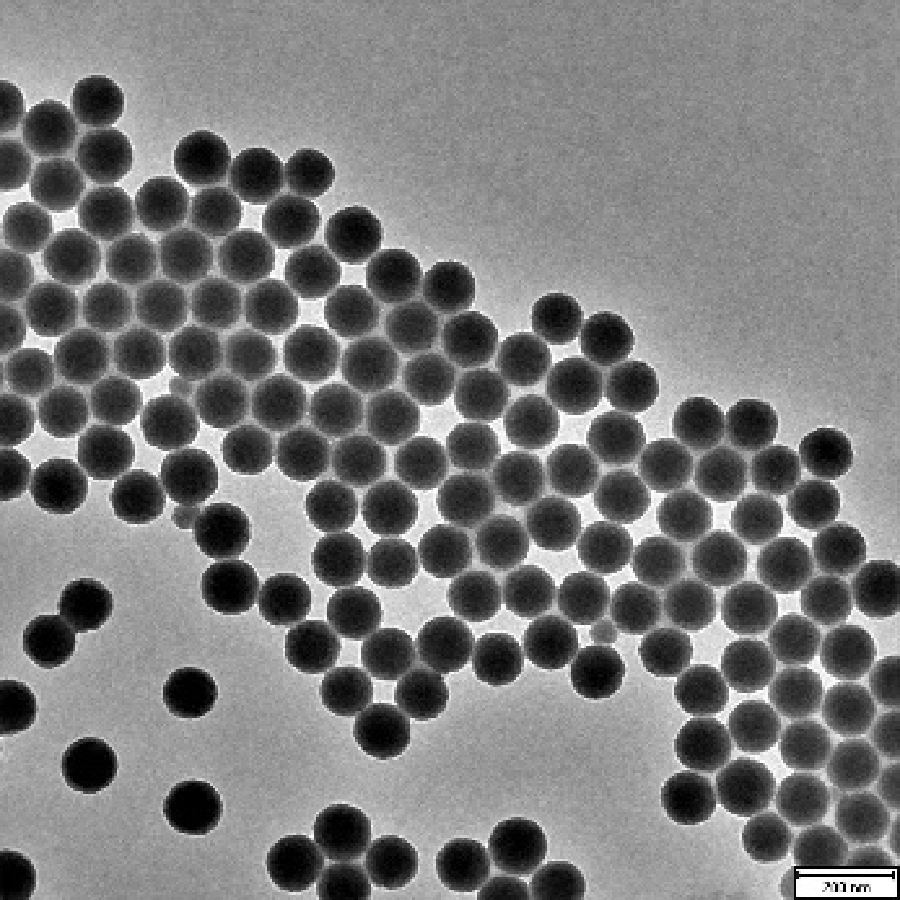

Silica sol can be used as the key raw material of CPM polishing liquid because silica sol is a dispersion of nano-silica particles. The nano-particles have good sphericity and the hardness of silica sol particles is appropriate, which can greatly reduce the scratches on the device during the polishing process. According to current manufacturing technology, the diameter of nano-silica particles in silica sol can be controlled within the range of 10-150nm. Silica sols of different particle sizes will produce different removal rates, providing many options for the flattening process of chip manufacturing. Therefore, silica sol has become the preferred raw material for CMP polishing liquid in chip manufacturing.

Nano-silicon dioxide particles in silica sol

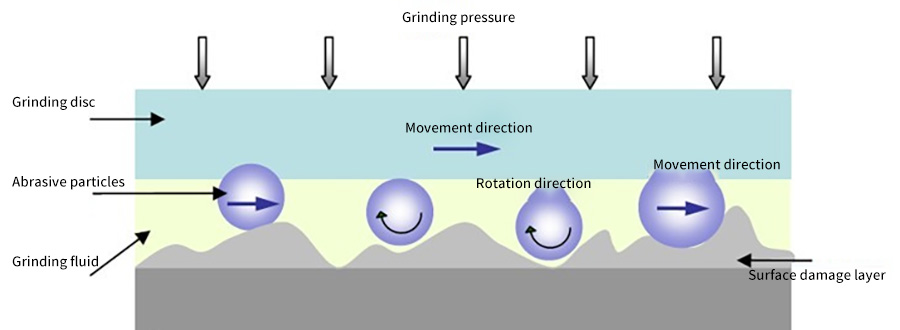

Schematic diagram of CPM polishing process

CMP stands for Chemical Mechanical Polishing, or chemical mechanical polishing, is like building a house. Each floor needs to be level and even before another floor can be built on top. Otherwise, the floor will be uneven, affecting the overall reliability. The technology used in chip manufacturing to make the floor flat is chemical mechanical polishing.

CMP is a process technology that flattens the surface of chip devices and makes it highly flat by organically combining the physical grinding action of nano-particles and the chemical corrosion action of polishing liquid. Currently, chip manufacturing mainly uses CMP technology to precisely polish the surface of the wafer, and can achieve a global flatness difference of 100A°~1000A° (equivalent to 10~100nm at the atomic level) with ultra-high flatness.

CMP is mainly used in the interlayer flattening of single-crystal silicon wafer polishing and multi-layer wiring metal interconnection structure processes. Integrated circuit manufacturing requires a series of physical and chemical operations on single-crystal silicon wafers. At the same time, as the device feature size decreases, more production processes are required. The production process below 90nm requires more than 400 processes. In terms of polishing process, products of different processes require different polishing processes. The 28nm process requires 12 to 13 CMPs. After entering the 10nm process, the number of CMPs will double to 25 to 30.

Therefore, silica sol plays a key role in CMP polishing liquid as a nano-silicon dioxide dispersion with controllable particle size.

CMP polishing liquid used in chip manufacturing has strict requirements for silica sol. In addition to strict control of particle size, it also has strict requirements for its purity, requiring the content of metal impurities to be controlled at less than 1ppm. This is because the current chip manufacturing technology has reached 5nm precision. If the silica sol contains metal ion impurities such as sodium, potassium, and iron, it will contaminate the microcircuit in the chip, causing it to break down and be damaged during use. Therefore, the purity of the silica sol used in the chip polishing liquid requires that its metal ion content be controlled at the ppb level.